Россия

Россия

Россия

Москва, г. Москва и Московская область, Россия

УДК 004.8 Искусственный интеллект

Раскрыта актуальность семейства проводных компьютерных сетевых технологий Ethernet, используемых для передачи потоков данных в локальных, городских и глобальных сетях. Рассмотрена историческая ре-троспектива и эволюция развития технологий Ethernet. Показана роль циклического избыточного кодирования (CRC), которое широко применяется в протоколах передачи данных, включая Ethernet, для обнаружения ошибок в данных путем добавления специального кода к каждому блоку. Обоснован выбор типа кадра Ethernet II как наиболее распространенного для передачи данных в локальных сетях. Исследована структура данных кадра Ethernet II, содержащая преамбулу, сетевые адреса получателя и отправителя, сведения о версии интернет-протокола, поле данных переменной длины от 46 до 1 500 байт и CRC. Описан принцип вычисления 4-х байт CRC для структуры данных кадра Ethernet II по 32-битному полиному 0x04C11DB7. Разработаны функциональная схема и алгоритм моделирования CRC-кодера. На языке программирования Verilog создан исходный код CRC-кодера, использующий функцию отражения битов для вычислений посредством обратного полинома 0xEDB88320. Разработана специальная программа для тестирования кодера, формирующая поток кадров Ethernet II, состоящих из адресов получателя и отправителя, поля типа интернет-протокола, полезной нагрузки случайной длины и межкадрового интервала от 12 до 24 байт нулей. Проведено моделирование работы кодера в среде разработки ПЛИС Xilinx Vivado на потоке кадров Ethernet II, в которых отсутствует 8-байтовая преамбу-ла, т. к. она не учитывается при вычислении 32-битного CRC для кадра. Проведен анализ результирующих временных диаграмм. Выполнена проверка результатов вычислений в онлайн-калькуляторе CRC.

циклическое избыточное кодирование, программируемая логическая интегральная схема, Ethernet, обработка информации, вычисление

Введение

Ethernet – семейство проводных компьютерных сетевых технологий, используемых в локальных, городских и глобальных сетях [1, 2]. Ethernet был представлен в 1980 г. и впервые стандартизирован в 1983 г. как IEEE 802.3, затем усовершенствован для поддержки более высоких скоростей передачи данных, большего количества узлов и больших расстояний соединения [3, 4]. Со временем Ethernet в значительной степени заменил конкурирующие технологии проводной локальной сети, такие как Token Ring, FDDI и ARCNET [5].

Обнаружение ошибок играет ключевую роль в обеспечении целостности и надежности передаваемых данных в сетевых системах, таких как Ethernet. Одним из наиболее распространенных методов обнаружения ошибок является использование циклического избыточного кодирования (CRC) [6], которое активно применяется в протоколах передачи данных, включая Ethernet, где используется 32-битный CRC-код (CRC32).

Циклическое избыточное кодирование используется для обнаружения ошибок в данных путем добавления специального кода к каждому блоку перед его передачей по сети. Код вычисляется на основе определенного полинома и позволяет эффективно обнаруживать ошибки, возникающие во время передачи.

Ethernet II является одним из наиболее распространенных стандартов для передачи данных в локальных сетях, определяющим структуру кадра для обмена информацией между устройствами [7]. Стандарт обеспечивает эффективное и надежное взаимодействие в сетях, в том числе благодаря использованию 32-битного CRC.

Современные сетевые технологии, такие как IoT и промышленный Ethernet, требуют высокой надежности передачи данных при ограниченных вычислительных ресурсах. В условиях высокой зашумленности каналов связи или при работе на устройствах с низким энергопотреблением (например, встраиваемых системах) традиционные методы контроля ошибок могут оказаться недостаточно эффективными. Данное исследование направлено на разработку оптимизированного CRC-кодера для программируемых логических интегральных схем (ПЛИС), который обеспечивает высокую скорость обработки данных при минимальных аппаратных затратах. Это особенно актуально для сегментов сетей, где критичны энергопотребление и быстродействие.

Во встраиваемых системах CRC-кодирование в большинстве случаев реализуется на ПЛИС в виде либо цифровых схем, либо программного кода на языках VHDL или Verilog [8]. Целью данной работы является создание и моделирование проекта ПЛИС 32-битного циклического избыточного кодера (CRC32) для кадров типа Ethernet II. Для достижения поставленной цели в работе решен комплекс задач:

– анализ структуры данных кадра Ethernet II и локализация в нем битов CRC;

– определение 32-битного полинома для кадра Ethernet II и принципа его вычисления;

– разработка функциональной схемы и алгоритма моделирования CRC-кодера;

– реализация исходного кода CRC-кодера на языке программирования Verilog на основе принципа вычисления CRC для кадра Ethernet II;

– проведение моделирования в среде разработки ПЛИС Xilinx Vivado, проверка результатов вычислений в онлайн-калькуляторе.

Анализ структуры данных кадра Ethernet II и принцип вычисления CRC

Кадры, или фреймы, Ethernet II (рис. 1) состоят из четко определенных полей, включая адреса отправителя и получателя, тип протокола и контрольные суммы, что позволяет обеспечить целостность и правильную интерпретацию передаваемых данных [9].

Рис. 1. Структура данных кадра Ethernet для моделирования

Fig. 1. Ethernet frame data structure for simulation

Кадр начинается с преамбулы SYNC длиной 8 байт, поля, содержащего MAC-адрес получателя (RECIEVER), длина которого составляет 6 байт. Этот адрес представляет собой уникальный идентификатор для каждого сетевого интерфейса, что обеспечивает точное адресное назначение в процессе передачи данных. MAC-адреса формируются производителем сетевого оборудования и записываются в микросхему сетевой карты, это гарантирует, что каждый адрес будет уникальным и не будет повторяться среди других устройств в сети. Зная MAC-адрес получателя, отправитель может уверенно передавать информацию, точно определяя, кому она предназначена.

MAC-адрес отправителя (SENDER) длиной 6 байт предоставляет информацию о том, откуда поступили данные, позволяя получателю узнать источник сообщения. Идентификация отправителя имеет решающее значение для обеспечения обратной связи и управления потоком данных в сети. Получив данные, устройство может использовать адрес отправителя для отправки ответов или запросов, а также для диагностики сетевых проблем и отслеживания соединений.

Поле Type, состоящее из 2 байт, используется операционной системой принимающей станции для выбора версии интернет-протокола, например IPv4. Самоидентифицирующиеся фреймы позволяют смешивать несколько протоколов в одной физической сети и использовать несколько протоколов совместно одному компьютеру.

Поле данных (PAYLOAD), которые передаются от отправителя к получателю, содержит фактические данные, включая различные типы информации, такие как текстовые сообщения, изображения, видео и другие формы цифрового контента. Размер PAYLOAD может варьироваться от 46 до 1 500 байт и изменяться в зависимости от типа передаваемой информации и требований конкретных сетевых протоколов, используемых в сети. Если размер данных меньше 46 байт, в кадр добавляются дополнительные байты для достижения минимального размера кадра.

Завершающим элементом кадра Ethernet II является поле CRC, которое состоит из 4 байт. Это поле обеспечивает проверку целостности данных, переданных в кадре. Принцип вычисления CRC основан на математических методах, позволяющих обнаруживать ошибки, возникающие в процессе передачи информации. по различным причинам, включая электрические помехи, проблемы с соединением или сбои в работе оборудования. Использование поля CRC значительно повышает надежность коммуникации, т. к. оно позволяет системе обнаруживать любые изменения в данных. Если принимающее устройство получает значение, отличное от указанного в поле CRC, это сигнализирует о том, что произошла ошибка в передаче.

В таком случае устройство может инициировать запрос на повторную передачу данных, что позволяет избежать потери информации и гарантирует, что получатель примет целостные данные.

CRC-кодирование базируется на делении данных, представленных в виде длинной битовой строки, на фиксированный полином. Процесс деления вычисляет остаток, который и служит контрольной суммой. Этот остаток добавляется к исходным данным и передается вместе с ними. Получатель выполняет аналогичное деление и проверяет совпадение вычисленной контрольной суммы с полученной. Несовпадение указывает на наличие ошибок в данных. В кадрах Ethernet II используется фиксированный полином 0x04C11DB7 для 32-битного CRC [9], который можно записать в виде функции P(x)

![]()

Деление на этот полином осуществляется с помощью операции XOR (исключающее ИЛИ), что делает процесс более эффективным для аппаратной реализации на ПЛИС, поскольку переносы в данном случае не учитываются. Процесс деления начинается с выравнивания полинома по левому краю двоичной строки данных. На каждом шаге текущий блок данных, длина которого соответствует длине полинома, делится на полином с использованием операции XOR. Результат этой операции затем применяется для выравнивания следующего блока данных. Процесс повторяется до тех пор, пока вся битовая строка не будет обработана. Если в конце остается неполный блок данных, его можно дополнить нулями до полной длины полинома, что позволяет обеспечить согласованность в длине.

После завершения всех операций деления конечный 32-битный остаток (CRC32) является контрольной суммой. CRC32 служит критически важным элементом для проверки целостности передаваемых данных. Перед передачей он добавляется к исходным двоичным данным, что позволяет как отправителю, так и получателю проверить, были ли данные искажены в процессе передачи.

Среди альтернативных полиномов для сравнительного анализа (табл.) можно выделить:

– CRC-16-CCITT (телекоммуникации):

![]()

– CRC-8-Dallas/Maxim (1-Wire протоколы, короткие сообщения в датчиках):

![]()

– Koopman-64 (критичные системы, файловые системы, распределенные хранилища данных):

![]()

Сравнительный анализ CRC-полиномов для Ethernet-кадров

Comparative analysis of CRC polynomials for Ethernet frames

|

Критерий |

CRC32 (Ethernet) |

CRC-16-CCITT |

CRC-8 |

Koopman-64 |

|

Полином (HEX) |

0x04C11DB7 |

0x1021 |

0xD5 |

0xAD93D23594C935A9 |

|

Степень полинома |

32 |

16 |

8 |

64 |

|

Контрольная сумма, байт |

4 |

2 |

1 |

8 |

|

Обнаружение ошибок: |

||||

|

Одиночные биты, % |

100 |

100 |

100 |

100 |

|

Двойные биты, % |

100 |

100 |

< 90 |

100 |

|

Пакеты до N бит |

N = 32 |

N = 16 |

N = 8 |

N = 64 |

|

Вычислительная сложность |

Средняя (оптимизировано для ПЛИС) |

Низкая |

Очень низкая |

Высокая |

|

Рекомендуемая |

≤ 1 500 |

≤ 256 |

≤ 64 |

Любая |

|

Ресурсы ПЛИС (LUT/FF) |

128/32 |

64/16 |

32/8 |

256/64 |

Предложенная реализация CRC32 на ПЛИС с использованием обратного полинома 0xEDB88320 и функций отражения битов обеспечивает высокую эффективность при минимальных аппаратных затратах. Это особенно важно для устройств с ограниченными вычислительными ресурсами.

Функциональная схема и алгоритм моделирования CRC-кодера

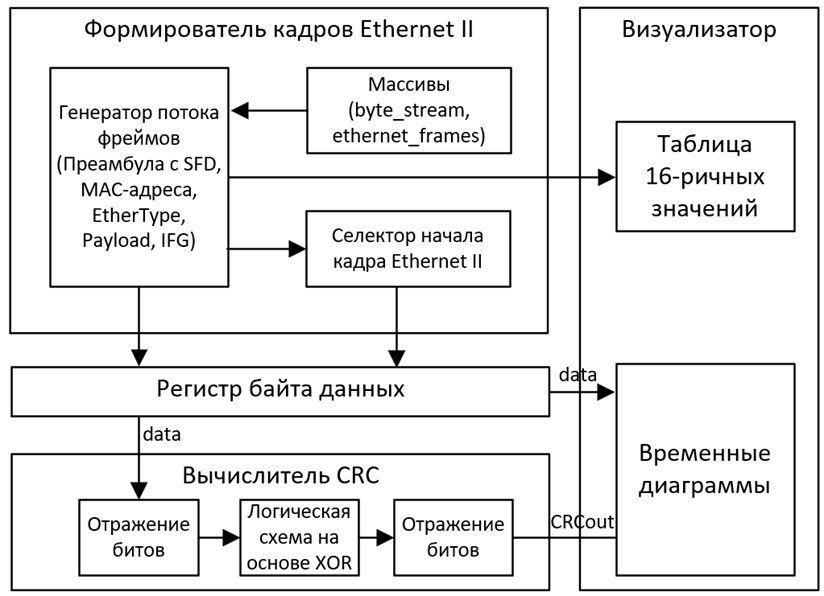

Функциональная схема моделирования кодера (рис. 2) с вычислением CRC32 для кадров Ethernet II состоит из формирователя кадров Ethernet II, вычислителя CRC и визуализатора.

Рис. 2. Функциональная схема моделирования CRC-кодера

Fig. 2. Functional scheme of CRC encoder modeling

Формирователь кадров Ethernet II в массивах byte_stream, ethernet_frames генерирует поток фреймов, содержащих преамбулу SYNC с последним байтом SFD, MAC-адреса, поля EtherType, Payload и межкадровый интервал IFG. По сигналу от селектора начала кадра Ethernet II данные потока побайтно (data) передаются в вычислитель CRC через регистр. Вычислитель CRC по полиному 0x04C11DB7, используя функции отражения битов на входе и выходе, реализует вычисление обратного полинома 0xEDB88320 от data на основе функций XOR. Генерируемые фреймы визуализируются в виде таблицы 16-ричных значений, а байты данных data и результирующие значения CRCout визуализируются в виде временных диаграмм в среде моделирования. Алгоритм моделирования CRC-кодера, представленный на рис. 3, включает операции по формированию кадров Ethernet II, вычислению CRC и визуализации этих процессов. После инициализации массивов byte_stream и ethernet_frames с их использованием генерируется поток кадров. Формируемый поток кадров Ethernet II состоит из случайного количества фреймов (от 10 до 35), причем каждый фрейм содержит преамбулу (7 байт 0x55) с SFD (1 байт 0xD5), случайные MAC-адреса (12 байт), случайный EtherType (2 байта, IPv4, ARP или IPv6), случайную Payload (от 46 до 1 500 байт) и межкадровые интервалы IFG (от 12 до 24 байт нулей). Перед передачей байта в вычислитель CRC согласно алгоритму моделирования осуществляется селекция начала кадра Ethernet II путем поиска преамбулы с SFD в потоке на входной линии. Затем выполняется копирование данных текущего фрейма в массив ethernet_frames без преамбулы с SFD, которые визуализируются в виде таблицы 16-ричных значений.

Рис. 3. Алгоритм моделирования CRC-кодера

Fig. 3. CRC encoder modeling algorithm

Данные фрейма из массива ethernet_frames побайтно (data) отражаются (reflected_data) с использованием функции reflect8 для вычисления итогового crcOut посредством функций XOR по обратному полиному 0xEDB88320, причем обратный полином формируется из исходного 0x04C11DB7 с использованием функции отражения битов reflect32. Текущие значения data и crcOut для кадра визуализируются на временных диаграммах.

Создание проекта ПЛИС и результаты моделирования работы CRC-кодера

В среде разработки ПЛИС Xilinx Vivado [10] был создан HDL-проект 32-битного CRC-кодера для кадра Ethernet II. Исходный код циклического избыточного кодера на языке Verilog размещен на открытом ресурсе GitHub [11] в составе двух файлов: вычислителя CRC32_module.v и тестовой программы CRC32_tb.v. Проект реализует принцип вычисления CRC32, который используется для проверки целостности данных в кадре Ethernet II. Процесс включает в себя последовательную обработку каждого байта данных [7 : 0] data, промежуточные вычисления посредством побитовой операции XOR и формирование итогового значения [31 : 0] crcOut. Причем входной байт данных [7 : 0] data и текущее значение [31 : 0] next_crc отражаются (биты переставляются в обратном порядке) с помощью функций reflect8 и reflect32. Поскольку исходный полином 0x04C11DB7 используется в обратном порядке битов, с помощью reflect32 он отражается в полином 0xEDB88320. Для моделирования кодера CRC32 в среде Xilinx Vivado на языке Verilog создана специальная тестовая программа crc32_tb, в которой формируется кадр Ethernet II со случайными значениями для MAC-адресов, Ethertype и Payload. В процессе тестирования кадр побайтно передается в модуль кодера CRC32, где для каждого байта вычисляется промежуточное значение CRC, а в результате выводится итоговое значение [31 : 0] crcOut. Исходный код тестовой программы crc32_tb. Тестовая программа crc32_tb выполняет моделирование процесса вычисления контрольной суммы CRC32 для входных данных, представленных в виде потока кадров Ethernet II. На этапе инициализации задается начальное значение 32'hFFFFFFFF регистра crcIn, а входной байт данных data инициализируется значением 8'h00, которое готовит модуль к вычислению контрольной суммы. Программа crc32_tb создает поток кадров Ethernet II со случайным количеством от 10 до 35. Каждый кадр состоит из преамбулы SYNC (7 байт 0x55)

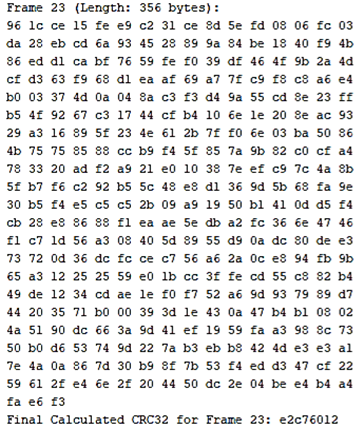

с начальным разделителем кадра SFD (1 байт 0xD5), случайных MAC-адресов (12 байт), случайного поля EtherType (2 байта: IPv4, ARP или IPv6), полезной нагрузки (Payload) случайной длины (от 46 до 1 500 байт) и межкадрового интервала (IFG, от 12 до 24 байт нулей). Поток байтов формируется в массиве byte_stream, после чего разделяется на отдельные фреймы. Результаты моделирования кодера в среде Xilinx Vivado в виде временных диаграмм, в виде консольного списка значений CRC в шестнадцатеричном формате, а также проверки этих значений в онлайн-калькуляторе CRC [12] представлены на рис. 4.

а

б в

Рис. 4. Результаты моделирования: временные диаграммы работы кодера CRC32 (а);

вывод значений в консоль Xilinx Vivado (б); проверка результатов моделирования в онлайн-калькуляторе (в)

Fig. 4. Simulation results: time diagrams of the CRC32 encoder (a);

output of values to the Xilinx Vivado console (б); verification of simulation results in an online calculator (в)

Так, при использовании CRC с полиномом 0x04C11DB7 при начальном регистре 32'hFFFFFFFF для одного из сгенерированных фреймов, содержащего случайные данные, был получен хеш 0xE2C76012, что подтверждается проверкой в онлайн-калькуляторе CRC.

Заключение

В современных протоколах Ethernet, включая гигабитный Ethernet и 10-гигабитный Ethernet, CRC32 играет важную роль в обеспечении целостности данных. Эти протоколы поддерживают высокие скорости передачи данных, и использование CRC32 остается эффективным решением для обнаружения ошибок при минимальных накладных расходах. Кроме того, современные сетевые устройства, такие как коммутаторы и маршрутизаторы, включают в себя аппаратные модули для вычисления CRC в реальном времени, что позволяет сократить задержки и снизить нагрузку на процессоры сетевых устройств. Это делает CRC32 одним из ключевых элементов обеспечения стабильной и надежной работы современных Ethernet-сетей. Завершающим элементом всех типов кадров Ethernet является поле контрольной суммы (CRC), состоящее из 4 байт, которое используется для проверки целостности данных в кадре. Главное преимущество CRC заключается в его способности эффективно обнаруживать одиночные и множественные ошибки в битах, а также пакетные ошибки, что делает его надежным средством контроля целостности данных. В кадре Ethernet II используется 32-битный CRC по полиному 0x04C11DB7. На основе принципа вычисления CRC и детализированного анализа структуры данных кадра Ethernet II и были разработаны функциональная схема и алгоритм моделирования CRC-кодера, обеспечивающие формирование потока кадров Ethernet II, вычисление 32-битного CRC по полиному 0x04C11DB7 с использованием операций XOR и визуализацию значений в среде моделирования. Проект циклического избыточного кодера, созданный в среде моделирования и разработки ПЛИС Xilix Vivado, содержит исходные коды вычислителя CRC и тестовой программы на языке программирования Verilog. Кодер из 8-битных входных данных реализует вычисление 32-битного значения CRC по полиному 0xEDB88320, который является побитовым отражением указанного в стандарте Ethernet II полинома 0x04C11DB7. Тестовая программа позволила провести моделирование процесса вычисления CRC на потоке кадров Ethernet II, состоящих из MAC-адресов, поля EtherType, полезной нагрузки Payload случайной длины (от 46 до 1 500 байт) и межкадрового интервала (IFG, от 12 до 24 байт нулей). При этом для упрощения моделирования 8-байтовая преамбула SYNС для кадра не задавалась, т. к. она не учитывается при вычислении CRC32. Полученные в результате моделирования значения были проверены в онлайн-калькуляторах CRC, и подтвердили правильность вычислений. Разработанный CRC-кодер демонстрирует высокую эффективность в условиях ограниченных ресурсов, что делает его применимым в таких областях, как промышленная автоматизация, IoT и телекоммуникации. Реализация на ПЛИС позволяет достичь высокой производительности при низком энергопотреблении, что особенно важно для устройств, работающих в условиях помех или с ограниченным энергопотреблением. Проведенный сравнительный анализ подтвердил преимущество использования полинома 0x04C11DB7 для кадров Ethernet II, а также показал, что предложенный алгоритм может быть адаптирован для других стандартов передачи данных.

1. Антонов А. И., Галкин В. А., Аксенов А. Н. Сетевые технологии в автоматизированных системах обработки информации и управления: учеб. пособие. М.: Изд-во МГТУ им. Н. Э. Баумана, 2020. 148 с.

2. Metcalfe R. M., Boggs D. R. Ethernet: distributed packet switching for local computer networks // Communi-cations of the ACM. 1983. V. 26. Iss. 1. P. 90–95. https://doi.org/10.1145/357980.358015.

3. Shoch J. F., Dalal Y. K., Redell D. D. Evolution of the Ethernet Local Computer Network // IEEE Computer. 1982. V. 15 (8). P. 14–26. DOI:https://doi.org/10.1109/MC.1982.1654107.

4. Spurgeon Ch. E., Zimmerman J. Ethernet: The Definitive Guide. O'Reilly Media, 2019. 508 p.

5. von Burg Urs, Kenney M. Sponsors, Communities, and Standards: Ethernet vs. Token Ring in the Local Area Networking Business // Industry & Innovation. 2003. V. 10 (4). P. 351–375. DOI:https://doi.org/10.1080/1366271032000163621. S2CID 153804163.

6. Press W. H., Teukolsky S. A., Vetterling W. T., Flannery B. P. Numerical Recipes: The Art of Scientific Computing. Cambridge University Press, 2007. 1195 p.

7. IEEE 802.3 'Standard for Ethernet' Marks 30 Years of Innovation and Global Market Growth (Press release). IEEE. June 24, 2013. URL: https://web.archive.org/web/20140112041706/http://standards.ieee.org/news/2013/802.3_30anniv.html (дата обращения: 12.03.2025).

8. Федоров И. К. Встраиваемые системы на основе ПЛИС: учеб. пособие. М.; СПб.: БХВ-Петербург, 2020. 576 с.

9. IEEE Std 802.3-2012, IEEE Standard for Ethernet. URL: https://standards.ieee.org/ieee/802.3/5084/ (дата обращения: 12.03.2025).

10. Аминев Д. А., Данилов Р. А. Моделирование на ПЛИС декодера кодов с малой плотностью проверок на четность на основе алгоритма минимальной суммы в среде разработки Xilinx Vivado // Проектирование и технология электронных средств. 2024. № 2. С. 30–39.

11. Захаржевский С. Ю. Исходный код проекта CRC кодера для Ethernet II // GitHub. 2025. URL: https://github.com/assah1/CRC32_Ethernet2/tree/main (дата обращения: 05.05.2025).

12. Онлайн-калькулятор для вычисления CRC. URL: https://crccalc.com/?crc=123456789&method=&datatype=0&outtype=0 (дата обращения: 05.05.2025).